CUSTOMER EDUCATION SERVICES

## **PrimeTime Workshop**

### **Lab Guide**

10-I-034-SLG-015

2018.06

**Synopsys Customer Education Services**

690 E. Middlefield Road

Mountain View, California 94043

Workshop Registration: <http://training.synopsys.com>

# Copyright Notice and Proprietary Information

© 2018 Synopsys, Inc. All rights reserved. This software and documentation contain confidential and proprietary information that is the property of Synopsys, Inc. The software and documentation are furnished under a license agreement and may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

## Destination Control Statement

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

## Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

## Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at <http://www.synopsys.com/Company/Pages/Trademarks.aspx>.

All other product or company names may be trademarks of their respective owners.

## Third-Party Links

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

Synopsys, Inc.

690 E. Middlefield Road

Mountain View, CA 94043

[www.synopsys.com](http://www.synopsys.com)

Document Order Number: 10-I-034-SLG-015

PrimeTime Lab Guide

# 1

# PrimeTime Flow

## Learning Objectives

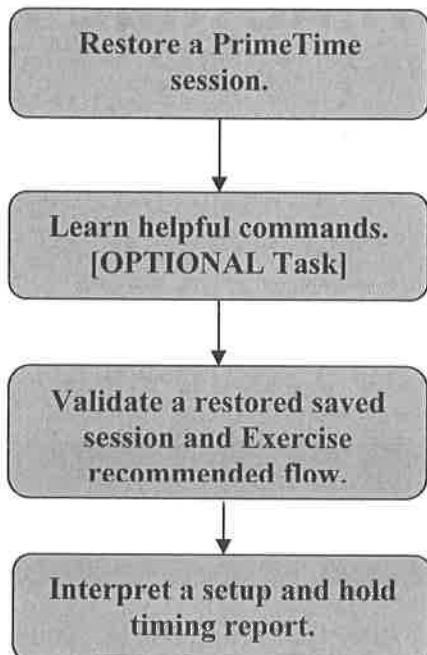

After completing this lab, you should be able to:

- Restore a previously saved PrimeTime session

- OPTIONAL, Take advantage of helpful PrimeTime commands that will make you more efficient when using PrimeTime interactively and show you how to find more information on commands, variables and your design library

- Validate a restored save-session.

- Exercise recommended Primetime flow

- Interpret key components of a timing report for setup and hold timing checks

**Lab Duration:**

45 minutes

## Lab 1

# Overview

## Relevant Files and Directories

All files for this lab are located in the `lab1_flow` directory under your home directory.

|                                 |                                    |

|---------------------------------|------------------------------------|

| <code>lab1_flow/</code>         | Current working directory          |

| <code>common_setup.tcl</code>   | multi-tool shared setup file       |

| <code>pt_setup.tcl</code>       | tool-specific PrimeTime setup file |

| <code>pt_scripts/</code>        | Run file directory                 |

| <code>pt.tcl</code>             | Run file                           |

| <code>.synopsys_pt.setup</code> | automatically-read PT setup file.  |

| <code>orca_savesession</code>   | Saved session directory            |

| <code>RUN.tcl</code>            | Run script for orca_savesession    |

## Answers / Solutions

This lab guide contains answers and solutions to all questions. If you need some help with answering a question or would like to confirm your results, check the back portion of this lab.

## Instructions

Your goal is to get used to PrimeTime by validating a restored save session, exercising the recommended flow, and analyzing the setup/hold reports.

### Task 1. Restore a PrimeTime Session

---

Invoke a previously saved PrimeTime session to perform STA.

1. Invoke PrimeTime from the `lab1_flow` workshop lab Unix directory.

```

unix% cd lab1_flow

unix% pt_shell

```

2. Restore a previously saved PrimeTime session. This step will read in the design netlist, libraries, and constraints. The design is now ready for analysis.

**Note:** The `orca_savesession` below is a Unix directory.

**Note:** The `orca_savesession` can be recreated, if needed, using: `pt_shell -f RUN.tcl | tee -i run.log`

**Note:** Any *PARA-124 Errors* during the execution of RUN.tcl can be safely ignored for the purpose of our labs.

**Note:** PrimeTime supports command, option, variable and file completion. Type a few letters and then hit the tab key.

```

pt_shell> restore_session orca_savesession

```

3. Generate coverage analysis report

```

pt_shell> report_analysis_coverage

```

**Question 1.** What is the name of the design under analysis?

.....

**Question 2.** How many *setup* and *hold* violations does **ORCA** have?

.....

4. Generate global timing report

## Lab 1

```

pt_shell> report_global_timing

```

**Question 3.** How many are reg-reg *setup* and *hold* violations?

.....

**Task 2. [OPTIONAL TASK] Explore Helpful Commands**

1. Execute the following three history short cut commands:

```

pt_shell> history

pt_shell> !!

pt_shell> !2

```

**Question 4.** Describe the difference between the last two history commands above.

.....

2. Use up and down arrows to scroll through the history event list as an alternative to the previous step.

Type the following to see all the available key bindings (in the default emacs editing mode).

```

pt_shell> list_key_bindings

```

3. Explore the **page mode** alias; execute the following command, which will generate a report that scrolls off the screen:

```

pt_shell> report_timing -group [get_path_group *]

```

4. Turn on page mode.

```

pt_shell> page_on

pt_shell> !rep

```

5. Use the **space bar** to page through a long report. Quit from a long report in page mode by typing “**q**”. If you want to turn off page mode, use the command alias **page\_off**.

6. Send a timing report to a separate window with the **view** Tcl procedure.

```

pt_shell> view report_timing -group [get_path_group *]

```

## Lab 1

7. Find the command to restore a PrimeTime session and then display help information on this command.

```

pt_shell> help restore*

pt_shell> man restore_session

pt_shell> restore_session -help

```

**Note:** The following is an alternative way to display syntax help.

```

pt_shell> help -v restore_session

```

**Question 5.** From the last command above, does the command **restore\_session** accept switches?

.....

8. The time unit in PrimeTime is determined by the main technology library. To find the time unit for **ORCA**, first list all libraries in memory.

**Note:** The \* in the following report indicates the main library.

```

pt_shell> list_lib

```

9. Generate a report for the main library which will state the time unit.

**Note:** Use copy and paste to avoid mistyping the lib name. The time unit is at the very top of the report.

```

pt_shell> report_lib cb13fs120_tsmc_max

```

**Question 6.** What is the time unit used for timing reports (as well as all other reports) for the **ORCA** design?

**Note:** Do not forget to use “q” to quit from a long report in page mode and return to the **pt\_shell** prompt without reading the entire report!

10. Display units used by the current design.

```

pt_shell> report_units

```

### Task 3. Validate an Existing PrimeTime Session

In this task, you will validate the inputs that have been read into PrimeTime: the current design and libraries, the backannotation and constraints.

1. Verify that the current design is your top-level module: ORCA

```

pt_shell> current_design

```

2. Compare the unix paths of the libraries to what has been read into PrimeTime

```

pt_shell> printvar search_path

pt_shell> printvar link_path

pt_shell> list_libraries

```

**Question 7.** Have the 4 libraries in the link\_path been successfully read into PrimeTime?

.....

**Question 8.** Which library defines the defaults for time units, operating conditions, and other delay calculation information?

.....

**Question 9.** What time unit is used?

.....

3. Verify that the nets are completely annotated.

```

pt_shell> report_annotated_parasitics

```

**Question 10.** Are there any nets that are not annotated?

.....

**Question 11.** What option to report\_annotated\_parasitics would be good to use as a 'next step' in debugging the missing nets?

.....

## Lab 1

4. Verify that the design is completely constrained.

```

pt_shell> check_timing

```

**Question 12.** What option to `check_timing` would be good to use as a ‘next step’ in debugging the missing constraints?

.....

5. Verify that the checks in your cells are completely exercised; look at possible causes for your findings.

```

pt_shell> report_analysis_coverage

pt_shell> report_case_analysis

```

**Question 13.** Is it logical that many of your timing checks are untested?

.....

6. Quit PrimeTime.

```

pt_shell> quit

```

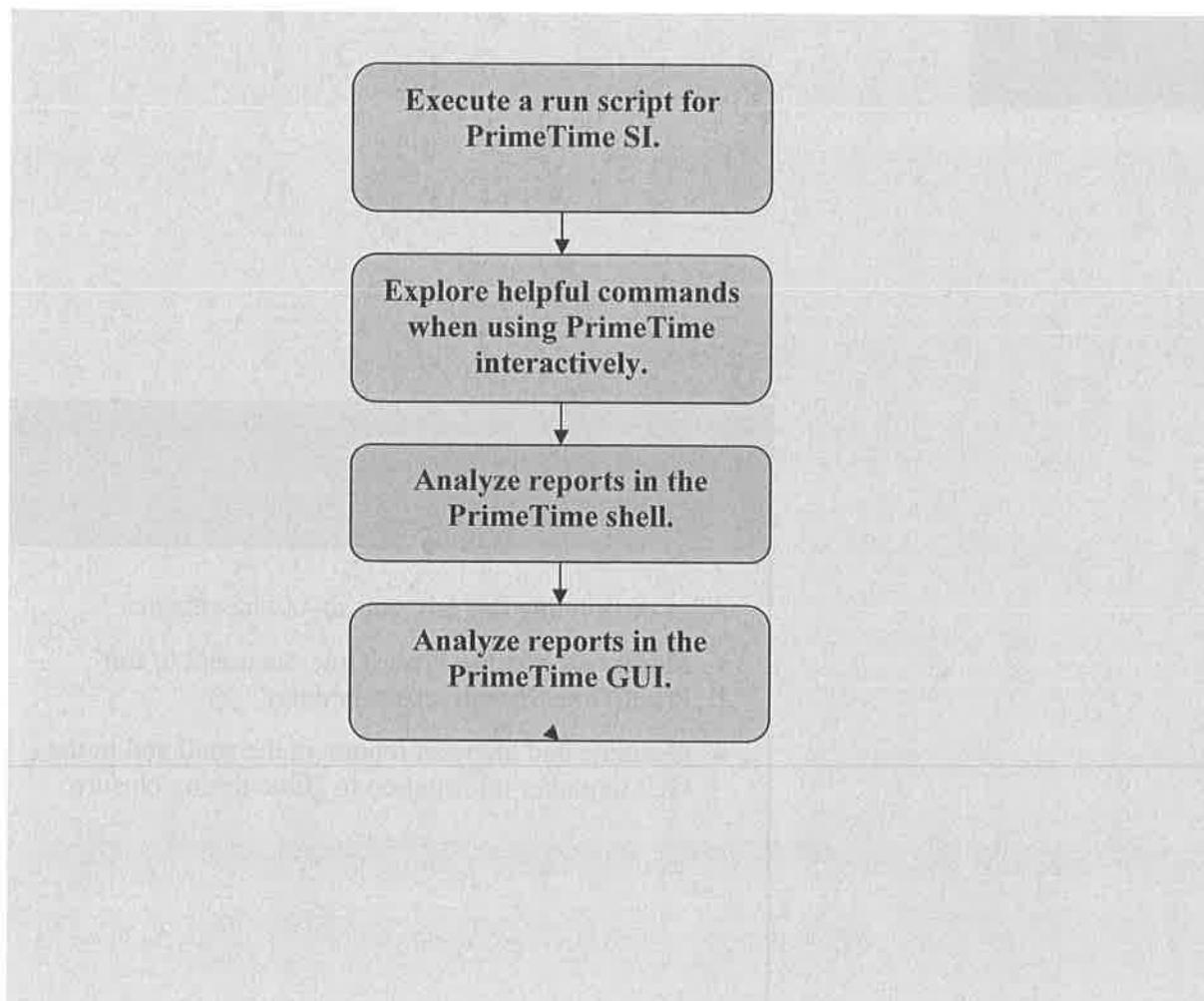

**Task 4. Execute the Run Script and Analyze the run**

---

1. Execute the run script logging the results to the log file `run.log`.

```

UNIX> pt_shell -f ./pt_scripts/pt.tcl | tee -i run.log

```

**Question 14.** Were there any errors during the execution of the run script?

.....

2. If there are any errors, address these first before moving on to the next step.

3. Evaluate your log file. With a text editor, open your log file. Search for the update timing messages (UITE-214), `print_message_info` output, and the `quit` output. Then, in your `profile` directory, examine the file `tcl_profile_sorted_by_cpu_time`.

**Question 15.** What step required the most CPU time?

.....

**Question 16.** What commands were causing UITE-214 messages?

.....

**Question 17.** Can any of the timing updates be avoided?

.....

**Question 18.** Why might the `quit` command output be a good place to start before reviewing your log file?

.....

## Lab 1

### Task 5. Analyze STA Reports

Generate and interpret two STA reports for setup and hold for **SYS\_CLK**.

1. Invoke PrimeTime and restore the session that you saved in the previous task

```

unix% pt_shell

pt_shell> restore_session my_savesession

```

2. Execute the following to display the clocks in **ORCA**:

```

pt_shell> report_clock

```

**Question 19.** How many clocks are in **ORCA**?

.....

3. Create a single, “short” timing report for setup for the clock **SYS\_CLK**. Use command-line expansion (the tab key) to expand both the command AND the options **-group** and **-path**.

```

pt_shell> report_timing -group SYS_CLK -path short

```

**Note:** The lines containing the data path cells and their delays are removed from the data arrival section making this report “short”.

**Note:** The above command generates a report for setup by default.

**Question 20.** There are at least 4 clues that this report is for setup and not for hold. How many can you identify?

.....

.....

**Question 21.** Identify the instance names of the start and end point flip-flops.

.....

**Question 22.** The clock skew for this timing path is 0.511ns; which two lines in the report can you use to calculate this?

.....

**Question 23.** How does this clock skew affect slack (i.e. does the clock skew help or hurt slack)?

.....

**Question 24.** How large is the violation in comparison to the clock period?

.....

4. Generate a timing report for hold time.

The following is a short cut that will execute the last command in history starting with the letters “**rep**” and add the switch **-delay min** (which will generate a report for hold time).

```

pt_shell> !rep -delay min

```

**Question 25.** There are at least 4 clues that indicate this is a hold report and not a setup report. How many can you find?

.....

**Question 26.** How does the clock skew in this hold report affect slack (i.e. does the clock skew help or hurt slack)?

.....

5. Quit PrimeTime.

```

pt_shell> quit

```

*This completes Lab 1. Return to lecture.*

## Answers / Solutions

**Question 1.** What is the name of the design under analysis?

The design is **ORCA**.

**Question 2.** How many *setup* and *hold* violations does **ORCA** have?

There are 23 setup and 53 hold violations.

**Question 3.** How many are **reg-reg setup** and **hold** violations?

There are 9 setup and 53 hold violations of type **reg-reg**.

**Question 4.** Describe the difference between the last two history commands above.

The command **! 2** repeats the 2<sup>nd</sup> command executed in history. The command **! !** repeats the last executed command in history.

**Question 5.** From the last command above, does the command **restore\_session** accept switches?

Yes, it accepts a session name, allowing a user to specify which of many saved sessions to restore.

**Question 6.** What is the time unit used for timing reports (as well as all other reports) for the **ORCA** design?

1ns.

**Question 7.** Have the 4 libraries in the **link\_path** been successfully read into PrimeTime?

Yes – the four libraries specified with **link\_library** are the same as those displayed with **list\_libraries**.

**Question 8.** Which library defines the defaults for time units, operating conditions, and other delay calculation information?

**cb13fs120\_tsmc\_max** – the asterisk to the left of the library (from **list\_libraries**) indicates ‘main library’

**Question 9.** What time unit is used?

```

pt_shell> report_lib cb13fs120_tsmc_max

*****

Report : library

Library: cb13fs120_tsmc_max

*****

Time Unit : 1 ns

```

```

pt_shell> report_units

*****

Report : units

Design : ORCA

*****

Units

-----

-

Capacitive_load_unit : 1e-12 Farad

Current_unit : 1e-06 Amp

Resistance_unit : 1000 Ohm

Time_unit : 1e-09 Second

```

**Question 10.** Are there any nets that are not annotated?

Yes: there are some internal driverless nets and some boundary pin-to-pin nets that are not annotated.

**Question 11.** What option to `report_annotated_parasitics` would be good to use as a 'next step' in debugging the missing nets?

`report_annotated_parasitics -help` shows options; the `-list_not_annotated` option shows the net names; you might want to focus in on the pin-to-pin nets by using the `-pin_to_pin_nets` option.

**Question 12.** What option to `check_timing` would be good to use as a 'next step' in debugging the missing constraints?

`check_timing -help` displays a list of options: the `-verbose` option lists the unconstrained endpoints

**Question 13.** Is it logical that many of your checks are untested?

Yes – `test_mode`, `scan_en`, and `power_save` are constrained off – performing STA on additional modes might enable more checks to be tested.

**Question 14.** Were there any errors during the execution of the run script?

No. The “run script” is setup such that any errors will terminate the script in the middle of execution. If the script completes, no errors occurred during execution of the run script. Moreover, from the “Diagnostics Summary” messages at the end of the log file from the `quit` command, there were no errors during the run.

**Question 15.** What step required the most CPU time?

For this lab, sourcing the constraints took the most CPU time.

**Question 16.** What commands were responsible for UITE-214 messages?

`update_timing -full` and a call to a macro `PLL_SHIFT` which invoked `update_timing`

**Question 17.** Can any of the timing updates be avoided?

Yes, there is an `update_timing` both before and after `set_propagated_clocks` – the one before `set_propagated_clocks` is unnecessary. One `update_timing` command is in `pt.tcl` – the other is in a constraint file (`orca_pt_other.tcl`) sourced by `orca_pt_constraints` which is sourced by `pt.tcl`

**Question 18.** Why might the `quit` command output be a good place to start before reviewing your log file?

It gives a high-level summary of potential trouble spots: messages, both warning and information, timing updates, and performance statistics.

**Question 19.** How many clocks are in ORCA?

There are 6 clocks in ORCA.

**Question 20.** There are at least 4 clues that this report is for setup and not for hold. How many can you identify?

The most glaring clue is the “library setup time” in the generated report. The more subtle clues are:

- The clock edges used for the data arrival and data required are 0ns and 8ns respectively (and not 0ns and 0ns as for hold time).

- The “Path Type” in the header is **max** which indicates that this report is for setup (a “Path Type” of **min** indicates a hold report).

- Finally, the data arrival time is after the data required time and the slack is violated (whereas if this was a report for hold, the slack would be met!)

**Question 21.** Identify the instance names of the start and end point flip-flops.

```

Startpoint: I_ORCA_TOP/I_BLENDER/s3_op2_reg[18]

(rising edge-triggered flip-flop clocked by SYS_CLK)

Endpoint: I_ORCA_TOP/I_BLENDER/s4_op2_reg[31]

(rising edge-triggered flip-flop clocked by SYS_CLK)

Path Group: SYS_CLK

Path Type: max

Min Clock Paths Derating Factor : 0.900

```

**Question 22.** The clock skew for this timing path is 0.511 ns. Which lines in the report can you use to calculate this?

| Point                                            | Incr    | Path     |

|--------------------------------------------------|---------|----------|

| clock SYS_CLK (rise edge)                        | 0.000   | 0.000    |

| clock network delay (propagated)                 | 3.247   | 3.247    |

| I_ORCA_TOP/I_BLENDER/s3_op2_reg[18] /CP (sdnrb1) | 0.000   | 3.247 r  |

| I_ORCA_TOP/I_BLENDER/s3_op2_reg[18] /Q (sdnrb1)  | 0.516 & | 3.763 r  |

| ...                                              |         |          |

| I_ORCA_TOP/I_BLENDER/s4_op2_reg[31] /D (sdnrb1)  | 8.242 & | 12.004 f |

| data arrival time                                |         | 12.004   |

| clock SYS_CLK (rise edge)                        | 8.000   | 8.000    |

| clock network delay (propagated)                 | 2.736   | 10.736   |

| ....                                             |         |          |

**Question 23.** How does this clock skew affect slack (i.e. does the clock skew help or hurt slack)?

The clock skew hurts the slack for setup in this specific timing report. The clock latency to the start point flip-flop causes the data to arrive 0.511ns later causing a larger setup timing violation..

**Question 24.** How large is the violation in comparison to the clock period?

The clock period is 8ns. The violation is 0.987. It is approximately 12% of the clock period.

**Question 25.** There are at least 4 clues that indicate this is a hold report and not a setup report. How many can you find?

The most glaring clue is the highlighted “library hold time” in the report below. The more subtle clues are:

- The clock edges used for the data arrival and data required are 0ns and 0ns respectively.

- The “**Path Type**” in the header is **min** which indicates that this report is for hold time.

- Finally, the data arrival time is before the data required time and the slack is violated.

**Question 26.** How does the clock skew for this hold report affect slack (i.e. does the clock skew help or hurt slack)?

From the report, you can see (after applying the clock network delay) that the capture clock edge arrives later than the launch clock edge. This hurts the hold slack, causing a violation.

| Point                                           | Incr    | Path    |

|-------------------------------------------------|---------|---------|

| clock SYS_CLK (rise edge)                       | 0.000   | 0.000   |

| clock network delay (propagated)                | 2.360   | 2.360   |

| I_ORCA_TOP/I_PARSER/out_bus_reg[10]/CP (sdcrq1) | 0.000   | 2.360 r |

| I_ORCA_TOP/I_PARSER/out_bus_reg[10]/Q (sdcrq1)  | 0.353 & | 2.713 r |

| ...                                             |         |         |

| I_ORCA_TOP/I_BLENDER/rem_green_reg/D (sdcrn1)   | 0.142 & | 2.855 f |

| data arrival time                               |         | 2.855   |

| clock SYS_CLK (rise edge)                       | 0.000   | 0.000   |

| clock network delay (propagated)                | 3.206   | 3.206   |

| clock reconvergence pessimism                   | -0.216  | 2.990   |

| I_ORCA_TOP/I_BLENDER/rem_green_reg/CP (sdcrn1)  |         | 2.990 r |

| library hold time                               | 0.006   | 2.997   |

| data required time                              |         | 2.997   |

| data required time                              |         | 2.997   |

| data arrival time                               |         | -2.855  |

| slack (VIOLATED)                                |         | -0.142  |

# 2

# Constraining Methodology

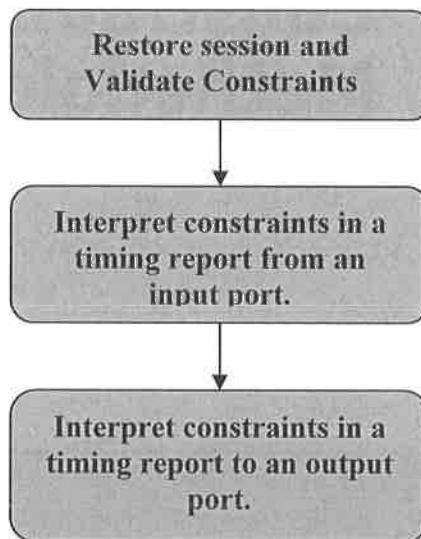

## Learning Objectives

After completing this lab, you should be able to:

- Validate constraints by checking for

- Constraint Completeness and

- Untested timing checks

- Identify and interpret constraints in a timing report

- Clock constraints

- Interface constraints

Lab Duration:

30 minutes

## Lab 2

# Overview

## Relevant Files and Directories

All files for this lab are located in the `lab2_constraints` directory under your home directory.

|                                 |                                 |

|---------------------------------|---------------------------------|

| <code>lab2_constraints/</code>  | Current working directory       |

| <code>orca_savesession/</code>  | Session to restore for labs     |

| <code>.synopsys_pt.setup</code> | PT setup file                   |

| <code>RUN.tcl</code>            | Run script for orca_savesession |

## Answers & Solutions

This lab guide contains answers and solutions to all questions. If you need some help with answering a question or would like to confirm your results, check the back portion of this lab.

# Instructions

## Task 1. Validate constraints

1. Invoke PrimeTime from the `lab2_constraints` directory and restore the PrimeTime session using the `orca_savesession` directory.

**Note:** The `orca_savesession` can be recreated, if needed, using: `pt_shell -f RUN.tcl | tee -i run.log`

**Note:** Any *PARA-124 Errors* during the execution of `RUN.tcl` can be safely ignored for the purpose of our labs.

2. Check for constraint completeness

```

pt_shell> check_timing -verbose

```

**Question 1.** Are all registers in the design clocked?

.....

**Question 2.** Are there any missing constraints? Can you explain?

.....

3. Check for the untested timing checks in the design

```

pt_shell> report_analysis_coverage

```

**Question 3.** Nearly two thirds of the setup/hold checks are untested! – What are the 2 causes?

.....

**Question 4.** Why are there unexercised `min_pulse_width` checks?

.....

**Question 5.** How many output delay constraints are there for setup and for hold and are these constraints met or violated?

.....

## Lab 2

### Task 2. Analyze a Timing Report For Input Delay Constraint

1. Generate a report for the input delay constraints applied to the port `pad[0]` .

```

pt_shell> report_port -input_delay pad[0]

```

**Question 6.** What are the min and max arrival times to `pad[0]` ?

.....

**Question 7.** What is the name of the external start point clock constraining `pad[0]` ?

.....

2. Generate a timing report for setup starting at the port `pad[0]` .

Answer the following questions using this report.

*Use your job aid labeled “timing reports” for help recalling the appropriate switch for report\_timing.*

**Question 8.** Which lines in the timing report did you use to ensure the reported path starts at the port `pad[0]` and is for setup?

.....

**Question 9.** List all user specified constraints in this timing report.

.....

**Question 10.** Where must the clock latency be included for the start point clock `PCI_CLK`?

.....

**Question 11.** Describe the direction of the port `pad[0]` (i.e. is it an input, output or inout port).

.....

**Question 12.** Describe the end point of this timing path (i.e. is it an output port or an internal flip-flop).

.....

3. Generate a new report from the same port `pad[0]` for setup, which also shows the details of the calculated clock network delay.

*Use the job aid labeled “timing reports” for help recalling the appropriate switch for `report_timing`. Remember to take advantage of `history` commands.*

**Question 13.** How large is the clock source latency versus the clock network latency for the end point clock `PCI_CLK`?

.....

**Question 14.** Where has the clock `PCI_CLK` been defined (the clock definition point)?

.....

4. Generate a report starting at the port `pad[0]` for hold time.

**Question 15.** Does the value of the input external delay constraint match your expectations?

.....

## Lab 2

### Task 3. Analyze a Timing Report For Output Delay Constraint

1. Generate a report for the output delay constraints applied to the port **pad[0]**.

**Question 16.** What are the min and max output delay constraints for this port?

.....

**Question 17.** How will the negative min output delay constraint be applied to this port (i.e. will it impose a positive or negative hold requirement)?

.....

**Question 18.** What is the name of the external end point clock constraining this port?

.....

2. Generate a “short” timing report ending at the port **pad[0]** for hold time.

**Question 19.** Describe the start point of this timing path (i.e. is it an input port or an internal flip-flop).

.....

**Question 20.** Does the path group for this timing path match your expectations?

.....

**Question 21.** Does the “data required time” match your expectations?

.....

3. Optionally, apply the following constraint which will impose a positive output delay constraint for hold on **pad[0]** and then re-execute the steps in this task to see the affect.

```

pt_shell> set_output_delay -min 1.0 -clock PCI_CLK pad[0]

```

Quit PrimeTime.

*This completes Lab2. Return to lecture.*

## Answers / Solutions

**Question 1.** Are all registers in the design clocked?

Yes. There are no clock pins reported following the message

Information: Checking 'no\_clock'.

**Question 2.** Are there any missing constraints? Can you explain?

Yes. There are 2 output ports reported to be missing their

output delays.

Warning: There are 2 endpoints which are not constrained for maximum

delay.

sd\_CKn

sd\_CK

The above warning can be ignored since these 2 are the

clock output ports (Use the **report\_clock** command to

confirm) that should not be constrained for output delay.

**Question 3.** Nearly two thirds of the setup/hold checks are untested! –

What are the 2 causes?

**constant\_disabled** and **false\_path**. (Using

**report\_analysis\_coverage -status**

**untested -check "setup hold"**)

**Question 4.** Why are there unexercised **min\_pulse\_width** checks?

**min\_pulse\_width** checks are exercised only if the pins

have clocks. Since these are non clock asynchronous pins

like "set or clear", no clocks have been defined on them.

(Use the command **report\_analysis\_coverage -status**

**untested -check min\_pulse\_width** to

confirm)

**Question 5.** How many output delay constraints are there for setup and

for hold and are these constraints met or violated?

From **report\_analysis\_coverage**, there are 75

output delay constraints for both setup and hold; 9 output

delay constraints for setup are violated; 39 output delay

constraints for hold are violated. Remember to verify that all

output ports are constrained for both setup as well as for

hold.

```

pt_shell> restore_session orca_savesession

pt_shell> report_analysis_coverage

```

| Type of Check   | Total | Met          | Violated  | Untested     |

|-----------------|-------|--------------|-----------|--------------|

| setup           | 9629  | 3575 ( 37%)  | 13 ( 0%)  | 6041 ( 63%)  |

| hold            | 9629  | 3517 ( 37%)  | 71 ( 1%)  | 6041 ( 63%)  |

| recovery        | 1316  | 1210 ( 92%)  | 0 ( 0%)   | 106 ( 8%)    |

| removal         | 1316  | 1204 ( 91%)  | 6 ( 0%)   | 106 ( 8%)    |

| min_period      | 20    | 20 (100%)    | 0 ( 0%)   | 0 ( 0%)      |

| min_pulse_width | 7273  | 5957 ( 82%)  | 0 ( 0%)   | 1316 ( 18%)  |

| out_setup       | 75    | 66 ( 88%)    | 9 ( 12%)  | 0 ( 0%)      |

| out_hold        | 75    | 36 ( 48%)    | 39 ( 52%) | 0 ( 0%)      |

| All Checks      | 29333 | 15585 ( 53%) | 138 ( 0%) | 13610 ( 46%) |

**Question 6.** What are the min and max arrival times to **pad[0]** ?

The min and max arrival times are 2ns and 8ns respectively (with the same constraint for both rise and fall data transitions at the port **pad[0]** ).

**Question 7.** What is the name of the external start point clock constraining **pad[0]** ?

The name of the clock is **PCI\_CLK**.

**Question 8.** Which lines in the timing report did you use to ensure the reported path starts at the port **pad[0]** and is for setup?

```

pt_shell> report_timing -from pad[0]

Startpoint: pad[0] (input port clocked by PCI_CLK)

Endpoint: I_ORCA_TOP/I_PCI_CORE/d_out_i_bus_reg[0]

(rising edge-triggered flip-flop clocked by PCI_CLK)

Path Group: PCI_CLK

Path Type: max

```

**Question 9.** List all user specified constraints involved in this timing report.

The clock period is a constraint. The clock **PCI\_CLK** is propagated (not ideal). The input external delay (which comes from an input delay constraint).

**Question 10.** Where must the clock latency be included for the start point clock **PCI\_CLK**?

The clock network delay is zero. Therefore, the only other place to represent the external clock latency is as a part of the input delay constraint (i.e. the input external delay). The appropriate way to model this is to use the switches **-network\_latency\_included** and **-source\_latency\_included** for **set\_input\_delay**.

**Question 11.** Describe the direction of the port **pad[0]** (i.e. is it an input, output or inout port).

The port **pad[0]** is an inout port; therefore, it is both a timing path start point as well as a timing path end point!

| Point                            | Incr  | Path    |

|----------------------------------|-------|---------|

| clock PCI_CLK (rise edge)        | 0.000 | 0.000   |

| clock network delay (propagated) | 0.000 | 0.000   |

| input external delay             | 8.000 | 8.000 r |

| <b>pad[0] (inout)</b>            | 0.000 | 8.000 r |

**Question 12.** Describe the end point of this timing path (i.e. is it an output port or an internal flip-flop).

The end point is a rising-edge triggered flip-flop clocked by **PCI\_CLK** (it is actually a timing model that looks like a flip-flop with setup and hold timing checks).

**Question 13.** How large is the clock source latency versus the clock network latency for the end point clock **PCI\_CLK**?

Shown below is only the data required time section of the timing report. The source latency is 0ns. The clock network latency is 0.768ns (15.768 – 15.000).

```

pt_shell> !rep -path full_clock

.

.

.

clock PCI_CLK (rise edge) 15.000 15.000

clock source latency 0.000 15.000

pclk (in) 0.000 15.000 r

pclk_iopad/CIN (pc3d01) 0.728 H 15.728 r

I_CLOCK_GEN/I_PLL_PCI/CLK (PLL) -1.220 H 14.508 r

I_CLOCK_GEN/bufbdfG1B1I1_1/Z (bufbdf) 0.184 & 14.692 r

I_CLOCK_GEN/U21/Z (mx02d2) 0.165 & 14.857 r

I_CLOCK_GEN/bufbdfG2B1I1_2/Z (bufbdf) 0.153 & 15.010 r

I_CLOCK_GEN/U17/ZN (invbdk) 0.076 & 15.086 f

I_CLOCK_GEN/U14/ZN (invbdk) 0.059 & 15.145 r

I_CLK_SOURCE_PCLK/Z (bufbdk) 0.168 & 15.313 r

invbd7G5B1I2/ZN (invbd7) 0.108 & 15.421 f

I_ORCA_TOP/invbdkG5B2I3_1/ZN (invbdk) 0.120 & 15.541 r

I_ORCA_TOP/I_PCI_CORE/buffd7G5B3I32/Z (buffd7) 0.140 & 15.680 r

I_ORCA_TOP/I_PCI_CORE/d_out_i_bus_reg[0]/CP (sdcrq1) 0.088 & 15.768 r

library setup time -0.153 15.615

data required time 15.615

```

**Question 14.** Where has the clock **PCI\_CLK** been defined (the clock definition point)?

The clock **PCI\_CLK** is defined at the input port **pclk**. The clock definition point separates the clock source latency from the clock network latency.

**Question 15.** Does the value of the input external delay constraint match your expectations?

Yes. From `report_port` above, the input external delay should be 2ns with respect to the rising edge of `PCI_CLK`. This is confirmed in the timing report below.

```

pt_shell> report_timing -delay min -from pad[0]

```

```

Startpoint: pad[0] (input port clocked by PCI_CLK)

Endpoint: I_ORCA_TOP/I_PCI_CORE/d_out_i_bus_reg[0]

(rising edge-triggered flip-flop clocked by PCI_CLK)

Path Group: PCI_CLK

Path Type: min

Min Data Paths Derating Factor : 0.900

Min Clock Paths Derating Factor : 0.900

```

| Point                            | Incr    | Path    |

|----------------------------------|---------|---------|

| clock PCI_CLK (rise edge)        | 0.000   | 0.000   |

| clock network delay (propagated) | 0.000   | 0.000   |

| input external delay             | 2.000   | 2.000 r |

| pad[0] (inout)                   | 0.000   | 2.000 r |

| pad_iopad_0/PAD (pc3b03)         | 0.044   | 2.044 r |

| pad_iopad_0/CIN (pc3b03)         | 0.662 & | 2.706 r |

**Question 16.** What are the min/max output delay constraints for this port?

```

pt_shell> report_port -help

```

Usage:

|                          |                                         |

|--------------------------|-----------------------------------------|

| <code>report_port</code> | # Report port info                      |

| [-verbose]               | (Show all port info)                    |

| [-design_rule]           | (Only port design rule info)            |

| [-drive]                 | (Only port drive info)                  |

| [-input_delay]           | (Only port input delay info)            |

| [-output_delay]          | (Only port output delay info)           |

| [-wire_load]             | (Only port wire load info)              |

| [-nosplit]               | (Don't split lines if column overflows) |

| [port_list]              | (List of ports)                         |

```

pt_shell> report_port -output_delay pad[0]

```

| Output Port | Output Delay |          |          |          | Related Clock | Related Pin |

|-------------|--------------|----------|----------|----------|---------------|-------------|

|             | Min Rise     | Max Fall | Min Rise | Max Fall |               |             |

| pad[0]      | -1.00        | -1.00    | 4.00     | 4.00     | PCI_CLK       | --          |

**Question 17.** How will the negative min output delay constraint be applied to this port (i.e. will it impose a positive or negative hold requirement)?

In lecture, it was stated that a negative hold output delay constraint will impose a positive hold requirement.

**Question 18.** What is the name of the external end point clock constraining this port?

The port **pad[0]** is constrained with respect to **PCI\_CLK**.

**Question 19.** Describe the start point of this timing path.

The start point of the timing path is an internal flip-flop.

```

pt_shell> report_timing -delay min -to pad[0]

Startpoint: I_ORCA_TOP/I_PCI_CORE/pad_out_buf_reg[0]

(rising edge-triggered flip-flop clocked

by PCI_CLK)

Endpoint: pad[0] (output port clocked by PCI_CLK)

```

**Question 20.** Does the path group for this timing path match your expectations?

Yes. The path group is **PCI\_CLK** which is the same as the external capture clock name.

**Question 21.** Does the “data required time” match your expectations?

Yes. The capture clock edge is zero, which is appropriate for hold. The hold requirement of 1ns is positive, and the propagated clock network delay is 0ns. The data required section of the timing report is shown below.

|                                  |       |       |

|----------------------------------|-------|-------|

| clock PCI_CLK (rise edge)        | 0.000 | 0.000 |

| clock network delay (propagated) | 0.000 | 0.000 |

| output external delay            | 1.000 | 1.000 |

| data required time               |       | 1.000 |

```

# Answers for optional step

pt_shell> report_port -output_delay pad[0]

Output Delay

Min           Max      Related Related

Output Port    Rise   Fall    Rise   Fall   Clock   Pin

-----

pad[0]          1.00  1.00   4.00   4.00  PCI_CLK   --

```

```

pt_shell> report_timing -to pad[0] -delay min -path short

.

.

.

Point                                Incr      Path

-----

clock PCI_CLK (rise edge)            0.000    0.000

clock network delay (propagated)    0.772    0.772

I_ORCA_TOP/I_PCI_CORE/pad_out_buf_reg[0]/CP (sdcrq1)

0.000    0.772 r

I_ORCA_TOP/I_PCI_CORE/pad_out_buf_reg[0]/Q (sdcrq1)  0.350 &  1.122 r

pad_out_buf_reg_0_ASTttcInst778/Z (bufbd4)        0.199 &  1.321 r

pad_iopad_0/PAD (pc3b03)            2.081 H   3.402 r

pad[0] (inout)                      0.044    3.445 r

data arrival time                  3.445

clock PCI_CLK (rise edge)            0.000    0.000

clock network delay (propagated)    0.000    0.000

clock reconvergence pessimism     0.000    0.000

output external delay             -1.000   -1.000

data required time                 -1.000

data arrival time                  -3.445

.

.

.

slack (MET)                         4.445

```

#From the above report, you can see that using a positive hold constraint

#for an output delay INCREASES the positive slack. This confirms that

#specifying a negative hold constraint for an output delay actually

#specifies the hold requirement on the output port.

This page is left blank intentionally.

# 3

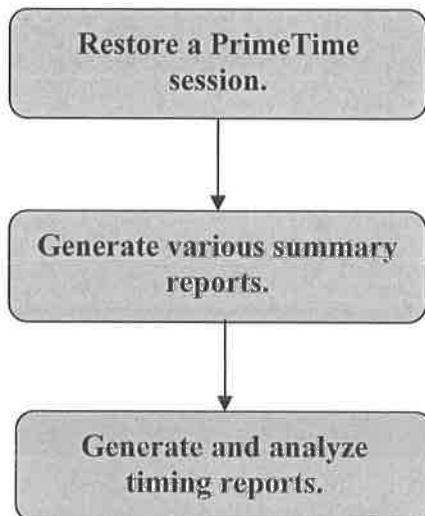

# Generating Reports

## Learning Objectives

After completing this lab, you should be able to:

- Generate summary reports for the violations in ORCA

- Analyze timing reports for setup and hold

- Apply the correct timing report switches

- Identify half clock cycle paths

Lab Duration:

45 minutes

## Lab 3

# Overview

## Relevant Files and Directories

All files for this lab are located in the `lab3_reports` directory under your home directory.

`lab3_reports/`

Current working directory

`orca_savesession/`

Session to restore for labs

`.synopsys_pt.setup`

PT setup file

## Answers & Solutions

This lab guide contains answers and solutions to all questions. If you need some help with answering a question or would like to confirm your results, check the back portion of this lab.

# Instructions

## **Task 1. Setup PrimeTime For Lab 3**

---

1. Invoke PrimeTime from the `lab3_reports` (which is a symbolic link to the `lab2_constraints`) workshop lab directory.

Restore the PrimeTime session using the `orca_savesession` directory.

2. Find the variable that controls the significant digits for many reports and set it to 4 significant digits. [Hint: `aa significant`]

**Question 1.** What is this variable's default value? [Hint: man page]

.....

## Lab 3

### Task 2. Generate Summary Reports

---

From lab 1, we know that there are setup violations in **ORCA**.

1. Answer the following questions by generating the appropriate summary reports:

**Question 2.** Identify the top five setup violations with the worst slack. The required details are the endpoint names and the slack.

.....

**Question 3.** List the 2 clock domains that have violating setup timing paths, and the 5 clock domains that have violating hold timing paths (**ORCA** has 6 clock domains in total).

.....

**Question 4.** Identify how many hold violations are on input paths, how many on output paths, and how many are register-to-register violations.

.....

2. Generate a report for the worst slack for setup to each bit of a 16-bit bus ending at the output ports **sd\_DQ [0]** to **sd\_DQ [15]** (the output ports are all constrained by a single clock, **SD\_DDR\_CLK**).

**Question 5.** List the end point with the largest margin (the best slack).

.....

3. Generate a high-level overview of the quality of the design

**Question 6.** Which clock group has the highest number of violating paths?

.....

### Task 3. Analyze Timing Reports for Setup and Hold

1. Turn page mode on.

2. Execute the following command to generate a timing report for **PCI\_CLK**:

```

pt_shell> report_timing -group PCI_CLK

```

**Question 7.** Does this timing path meet or violate timing?

.....

**Question 8.** What type of timing path is this - internal flip-flop to flip-flop, input, or output timing path?

.....

3. Generate a timing report for hold time for the same clock group **PCI\_CLK**.

```

pt_shell> report_timing -group PCI_CLK -delay min

```

**Question 9.** What type of timing path is this - internal flip-flop to flip-flop, input, or output timing path?

.....

**Question 10.** How many cells are on the data path of this timing path?

.....

**Question 11.** The cell delay used for the clock pin (**CP**) to **Q** pin of the start point flip-flop is for a rise transition. Offer one possible reason why this results in a worse slack for hold than using the faster fall delay through this flip-flop?

.....

*In the next step, you will continue to explore and confirm your answer for the above question.*

**Question 12.** What additional information do you need to confirm your answer for the above question?

.....

## Lab 3

4. Generate another timing report for the same timing path for hold time but with a fall transition at the end point (instead of a rise transition).

*Use copy and paste to avoid mistyping the end point and start point pin names.*

*Use the job aid labeled “timing reports” to find the appropriate switches for report\_timing.*

**Question 13.** Which lines in this report did you use to confirm that the correct path has been reported?

.....

**Question 14.** Was the guess correct – the faster fall delays results in a faster data arrival time but a smaller hold time requirement and thus a better slack?

.....

## Task 4. Apply the Correct Timing Report Switches

---

1. Answer the following questions by experimenting and exploring in PrimeTime.

*Use the job aid labeled “timing reports” for help identifying the appropriate commands and switches.*

**Question 15.** Write the command to generate a single timing report for each path group for setup.

.....

**Question 16.** Write the command to generate a single timing report for setup for each path group which has a violation.

.....

**Question 17.** What are the names of the two path groups that have violating timing paths in ORCA (the answer will come from the result of the previous question)?

.....

**Question 18.** Write the command to generate a timing report with the worst slack for setup to any output port constrained by the clock **PCI\_CLK**.

.....

**Question 19.** There are a few latches in ORCA; write the command to identify the data pins of these latches.

.....

**Question 20.** Write the command to generate a timing report for hold to the **D** pin of the **latched\_clk\_en\_reg** latches.

.....

## Lab 3

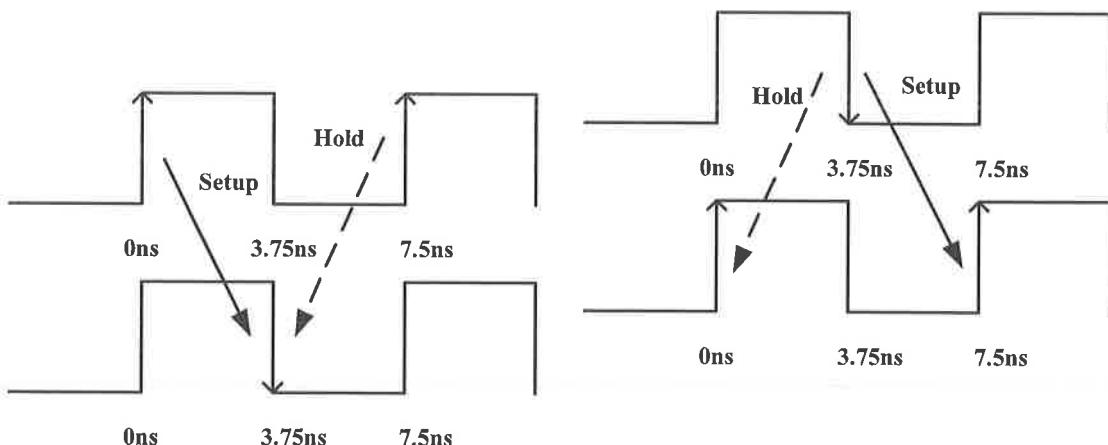

### Task 5. Identify Half-Clock Cycle Paths

The clock **SDRAM\_CLK** constrains many half clock cycle paths in **ORCA** (i.e. it constrains paths from a falling edge triggered flip-flop to a rising edge triggered flip-flop and vice versa).

These paths must be carefully monitored for various reasons (e.g. the duty cycle of **SDRAM\_CLK** is not yet well defined or for analysis of the clock skew).

1. Execute the following command to report the clock period for **SDRAM\_CLK** and use this information to answer the following questions:

```

pt_shell> report_clock SDRAM_CLK

```

**Question 21.** Given that the first number under the waveform column is the first rising edge for the clock **SDRAM\_CLK** and the second number is the falling edge – what duty cycle has been defined for this clock?

.....

**Question 22.** Describe the specific clock edges that will be used in a timing report for setup for a timing path constrained by the rising edge of **SDRAM\_CLK** to the falling edge of **SDRAM\_CLK**.

.....

**Question 23.** For this same timing path, describe the specific clock edges that will be used in a timing report for hold timing checks.

.....

2. Confirm the information in the following table by generating the appropriate timing reports for the half clock cycle timing paths constrained by the clock **SDRAM\_CLK**.

| Launch clock edge | Capture clock edge | Worst Setup Slack | Launch clock edge | Capture clock edge | Worst Hold Slack |

|-------------------|--------------------|-------------------|-------------------|--------------------|------------------|

| Rise 0ns          | Fall 3.75ns        | 0.680ns           | Rise 7.5ns        | Fall 3.75ns        | 3.558ns          |

| Fall 3.75ns       | Rise 7.50ns        | 0.635ns           | Fall 3.75ns       | Rise 0ns           | 3.514ns          |

**Question 24.** Which switch is useful for generating the worst 10 timing reports for each of these half clock cycle timing paths?

.....

**Question 25.** Why does PrimeTime report “no constrained paths?” (hint – the options PrimeTime is using are shown immediately following the `report_timing` command)

.....

**Question 26.** What additional option must you use to report the worst 10 timing paths?

.....

3. Quit PrimeTime.

*This completes Lab 3. End of Day-1.*

## Answers / Solutions

**Question 1.** What is this variable's default value?

```

set_app_var report_default_significant_digits -default

→ report_default_significant_digits = "2"

pt_shell> set report_default_significant_digits 3

```

**Question 2.** Identify the top five setup violations with the worst slack. The details that are required are the endpoint names and the slack.

The following command will list all setup violations sorted by slack. Use page mode to quit from the long report because the only information desired are the top 5 violations.

```

# No need to type the entire command name!

pt_shell> report_analysis -status violated -check setup -nosplit

```

| Constrained Pin                       | Related Pin | Check Clock Type | Slack         |

|---------------------------------------|-------------|------------------|---------------|

| I_ORCA_TOP/I_BLENDER/s4_op2_reg[31]/D | CP(rise)    | SYS_CLK          | setup -0.9872 |

| I_ORCA_TOP/I_BLENDER/s4_op1_reg[31]/D | CP(rise)    | SYS_CLK          | setup -0.8410 |

| I_ORCA_TOP/I_BLENDER/s4_op2_reg[30]/D | CP(rise)    | SYS_CLK          | setup -0.8305 |

| I_ORCA_TOP/I_BLENDER/s4_op1_reg[15]/D | CP(rise)    | SYS_CLK          | setup -0.6918 |

| I_ORCA_TOP/I_BLENDER/s4_op1_reg[30]/D | CP(rise)    | SYS_CLK          | setup -0.6843 |

**Question 3.** List the 2 clock domains that have violating setup timing paths, and the 5 clock domains that have violating hold timing paths (ORCA has 6 clock domains in total). (the following answer just shows the path group headers – the names of the endpoints have been removed to conserve space.

```

pt_shell> report_constraint -all_violators \

-max_delay -min_delay

max_delay/setup ('PCI_CLK' group)

max_delay/setup ('SYS_CLK' group)

min_delay/hold ('PCI_CLK' group)

min_delay/hold ('SDRAM_CLK' group)

min_delay/hold ('SD_DDR_CLK' group)

min_delay/hold ('SYS_2x_CLK' group)

min_delay/hold ('SYS_CLK' group)

```

**Question 4.**

Identify how many hold violations are on input paths, how many on output paths, and how many are register-to-register violations.

```

pt_shell> report_global_timing

Hold violations

-----

Total    reg->reg in->reg reg->out in->out

-----

WNS      -0.4375  -0.1420 -0.2363 -0.1281  -0.4375

TNS      -12.6317 -3.5616 -2.5768 -0.5954  -5.8979

NUM      100       59       18       7       16

```

**Question 5.** List the end point with the largest margin (the best slack).

The output port **sd\_DQ[0]** has the largest margin at 1.5994ns.

*Generally, the following command will only generate a single report for every end point because nworst is, by default, 1 and there is only a single clock constraining every output port. However, because increasing the value of max\_paths causes an implicit slack\_lesser 0 to be used, and because all the slacks to this endpoint are positive, PrimeTime will not report any paths unless we change the value of slack\_lesser to a large positive number – in this case, 100.*

```

pt_shell> report_timing -path end -max 16 -slack_lesser 100 -to sd_DQ*

*****

Report : timing

-path_type end

-delay_type max

-slack_lesser_than 100.0000

-max_paths 16

-sort_by slack

Design : ORCA

Version: J-2014.06

Date   : Wed Jul 23 12:01:51 2014

*****

Endpoint          Path Delay    Path Required    CRP      Slack

sd_DQ[14] (inout) 8.4133 f    9.6649        0.2418   1.4933

sd_DQ[6]  (inout) 8.4133 f    9.6649        0.2418   1.4934

sd_DQ[5]  (inout) 8.4133 f    9.6649        0.2418   1.4934

sd_DQ[4]  (inout) 8.4133 f    9.6649        0.2418   1.4934

sd_DQ[3]  (inout) 8.4133 f    9.6649        0.2418   1.4934

sd_DQ[10] (inout) 8.4112 f    9.6649        0.2418   1.4955

sd_DQ[15] (inout) 8.4111 f    9.6649        0.2418   1.4955

sd_DQ[13] (inout) 8.4111 f    9.6649        0.2418   1.4955

sd_DQ[12] (inout) 8.4111 f    9.6649        0.2418   1.4955

sd_DQ[9]  (inout) 8.4111 f    9.6649        0.2418   1.4955

sd_DQ[11] (inout) 8.4106 f    9.6649        0.2418   1.4960

sd_DQ[2]  (inout) 8.4054 f    9.6649        0.2418   1.5013

sd_DQ[1]  (inout) 8.4054 f    9.6649        0.2418   1.5013

sd_DQ[8]  (inout) 8.4032 f    9.6649        0.2418   1.5035

sd_DQ[7]  (inout) 8.4032 f    9.6649        0.2418   1.5035

sd_DQ[0]  (inout) 8.0654 f*   9.6649        0.0000   1.5994

```

**Question 6.** Which clock group has the highest number of violating paths?

```

report_qor -only_violated

```

SDRAM\_CLK has 30 violating paths

**Question 7.** Does this timing path meet or violate timing?

It violates timing with a slack of -1.157ns.

**Question 8.** What type of timing path is this - internal flip-flop to flip-flop, input, or output timing path?

This is an output timing path ending at the output port named **pad[1]**.

**Question 9.** What type of timing path is this - internal flip-flop to flip-flop, input, or output timing path?

This is an internal timing path. The end point looks like a flip-flop, but is one of many timing arcs in a RAM timing model.

**Question 10.** How many cells are on the data path of this timing path?

There is only one cell on this data path, the start point flip-flop. The timing path consists of a start point flip-flop tied directly to the end point flip-flop.

**Question 11.** The cell delay used for the clock pin (**CP**) to **Q** pin of the start point flip-flop is a rise delay. Offer one reason why this would result in a worse slack for hold than using a fall delay through this flip-flop?

Typically, fall delays are faster than rise delays and would offer a worse slack for hold! The one exception is if the fall delay at the data pin of the end point flip-flop resulted in a smaller library hold time requirement. This is what occurs in this case.

**Question 12.** Write the command to generate a single timing report for each path group for setup.

```

pt_shell> report_timing -group [get_path_group *]

```

**Question 13.** What additional information do you need to confirm your answer for the above question?

Generate another timing report where the data arrival time is calculated with fall transition at the end point and compare the two reports. In this way you can confirm that the library hold time is in fact smaller with a falling transition at the data pin of the end point flip-flop and thus the resulting slack better. You will explore this in the next lab step.

**Question 14.** Which lines in this report did you use to confirm that the correct path has been reported?

**Note:** The backslash in the command below is a line continuation character.

```

pt_shell> report_timing -delay min_fall \

-to I_ORCA_TOP/I_PCI_READ_FIFO/PCI_RFIFO_RAM/A1[1] \

-from I_ORCA_TOP/I_PCI_READ_FIFO/count_int_reg[1]1/CP

```

```

Startpoint: I_ORCA_TOP/I_PCI_READ_FIFO/count_int_reg[1]1

(rising edge-triggered flip-flop clocked by PCI_CLK)

Endpoint: I_ORCA_TOP/I_PCI_READ_FIFO/PCI_RFIFO_RAM

(rising edge-triggered flip-flop clocked by PCI_CLK)

Path Group: PCI_CLK

Path Type: min

Min Data Paths Derating Factor : 0.900

Min Clock Paths Derating Factor : 0.900

```

| Point                                                     | Incr    | Path    |

|-----------------------------------------------------------|---------|---------|

| clock PCI_CLK (rise edge)                                 | 0.000   | 0.000   |

| clock network delay (propagated)                          | 0.779   | 0.779   |

| I_ORCA_TOP/I_PCI_READ_FIFO/count_int_reg[1]1/CP (sdcrq1)  | 0.000   | 0.779 r |

| I_ORCA_TOP/I_PCI_READ_FIFO/count_int_reg[1]1/Q (sdcrq1)   | 0.344 & | 1.123 f |

| I_ORCA_TOP/I_PCI_READ_FIFO/PCI_RFIFO_RAM/A1[1] (ram32x32) | 0.016 & | 1.139 f |

| data arrival time                                         |         | 1.139   |

| clock PCI_CLK (rise edge)                                 | 0.000   | 0.000   |

| clock network delay (propagated)                          | 1.088   | 1.088   |

| clock reconvergence pessimism                             | -0.274  | 0.814   |

| I_ORCA_TOP/I_PCI_READ_FIFO/PCI_RFIFO_RAM/CE1 (ram32x32)   | 0.814   | r       |

| library hold time                                         | 0.211 * | 1.025   |

| data required time                                        |         | 1.025   |

| data required time                                        |         | 1.025   |

| data arrival time                                         |         | -1.139  |

| slack (MET)                                               |         | 0.114   |

**Question 15.** Was the guess correct – the faster fall delays results in a faster data arrival time but a smaller hold time requirement and thus a better slack?

Yes! The data arrival time is faster (1.139ns versus 1.150ns) but the hold time requirement is smaller (0.211ns versus 0.411ns) thus the slack is better than the original

timing report. Recall that hold time (and setup time) are a function of the transition at the data pin of the flip-flop.

**Question 16.** Write the command to generate a single timing report for setup for each path group which has a violation.

```

pt_shell> report_timing -group [get_path_group *]

-slack_lesser_than 0

# When using PrimeTime interactively - abbreviate

# command names or switches by typing enough letters to

# distinguish from other commands or switches - or,

# better yet, use command expansion by pressing tab

pt_shell> report_timing -slack_less 0

```

**Question 17.** What are the names of the two path groups that have violating timing paths in **ORCA** (the answer will come from the result of the previous question)?

The two path groups are **PCI\_CLK** and **SYS\_CLK**.

**Question 18.** Write the command to generate a timing report with the worst slack for setup to any output port constrained by the clock **PCI\_CLK**.

```

pt_shell> help all_*

pt_shell> all_outputs -help

pt_shell> report_timing -to [all_outputs -clock PCI_CLK]

# Or, another way to do the same thing

pt_shell> report_timing -to [all_outputs] -group PCI_CLK

```

**Question 19.** There are a few latches in **ORCA**; write the command to identify the data pins of these latches.

```

pt_shell> all_registers -level_sensitive -data_pins

```

**Question 20.** Write the command to generate a timing report for hold to the D pin of the **latched\_clk\_en\_reg** latches.

```

# Use copy and paste to avoid mistyping the long end point pin name

pt_shell> report_timing -delay min \

-to I_ORCA_TOP/I_BLENDER*/latched_clk_en_reg/D

```

**Question 21.** Given that the first number under the waveform column is the first rising edge for the clock **SDRAM\_CLK** and the second number is the falling edge – what duty cycle has been defined for this clock?

The rising edge of **SDRAM\_CLK** is at 0ns, the falling edge at 3.75ns and the period is 7.50ns. The duty cycle is 50%.

**Question 22.** Describe the specific clock edges that will be used in a timing report for setup for a timing path constrained by the rising edge of **SDRAM\_CLK** to the falling edge of **SDRAM\_CLK**.

Use the following clock waveform for this and the next question. The clock edges will be 0ns to 3.75ns.

**Question 23.** For this same timing path, describe the specific clock edges that will be used in a timing report for hold timing checks.

The clock edges will be 7.5ns to 3.75ns.

```

# Commands for the final task

# The backslash is a line continuation character

# The switch -delay min_max will generate one report for setup and

# one for hold

report_timing -rise_from [get_clocks SDRAM_CLK] \

-fall_to [get_clocks SDRAM_CLK] -delay_type min_max

report_timing -fall_from [get_clocks SDRAM_CLK] \

-rise_to [get_clocks SDRAM_CLK] -delay_type min_max

```

**Question 24.** Which switch is useful for generating the worst 10 timing reports for each of these half clock cycle timing paths?

The switch **-max\_paths 10** to the above command.

**Question 25.** Why does PrimeTime report “no constrained paths?”

The **-max\_paths** option implicitly sets another option: **slack\_lesser\_than 0**, which, because slack is positive, results in no constrained paths.

**Question 26.** What additional option must you use to report the worst 10 timing paths?

Since there are no violating paths that could be reported in this case, add the option: **slack\_less\_than 100**

This page is left blank intentionally.

# 4

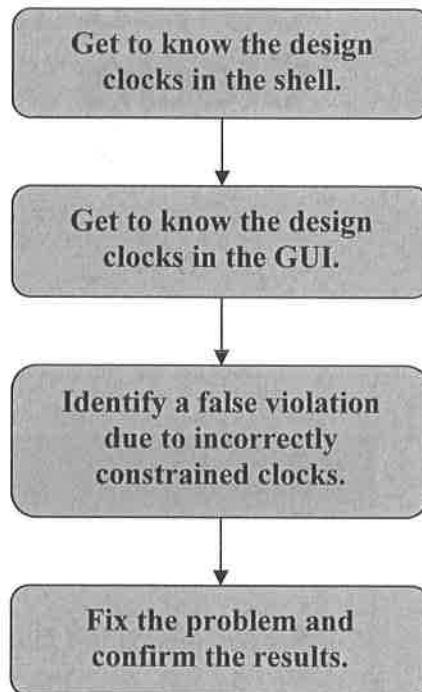

# Constraining Multiple Clocks

## Learning Objectives

After completing this lab, you should be able to:

- Apply the commands taught in lecture to gather information about the design clocks

- Use the GUI for another view of the design clocks and their relationships

Lab Duration:

45 minutes

## Lab 4

# Overview

## Relevant Files and Directories

All files for this lab are located in the `lab4_clocks` directory under your home directory.

|                                           |                                  |

|-------------------------------------------|----------------------------------|

| <code>lab4_clocks/</code>                 | Current working directory        |

| <code>orca_savesession/</code>            | Initial Saved ORCA session       |

| <code>orca_savesession_violations/</code> | Saved ORCA session with an issue |

| <code>RUN.tcl</code>                      | Run script for ORCA              |

| <code>.synopsys_pt.setup</code>           | PT setup file                    |

| <code>scripts/</code>                     |                                  |

| <code>orca_pt_variables.tcl</code>        | Variable script                  |

# Instructions

## **Task 1. Get to Know the Design Clocks**

---

1. Make sure your current directory is `lab4_clocks`

2. Invoke PrimeTime (pt\_shell).

Restore the session saved in `./orca_savesession`

*Take advantage of command and file name completion by typing a few letters and then using the tab key.*

3. Use the commands taught in lecture to answer the following questions.

*Use the job aid labeled “Clocks and More” for help recalling the specific commands.*

**Question 1.** How many clocks are in this design and how many of these are generated?

.....

**Question 2.** Which input ports have defined, master clocks?

.....

**Question 3.** Which output ports have defined, outgoing clocks?

.....

**Question 4.** Are the clocks propagated or ideal?

.....

**Question 5.** Which 3 clock pairs have constrained timing paths?

.....

## Lab 4

### Task 2. Use the GUI to Report Clock Relationships

If your design has many clocks, the GUI may simplify the task of understanding how the clocks are related.

1. Start the GUI by executing the following command.

```

pt_shell> start_gui

```

**Note:** The original pt\_shell session is still running in the terminal window. You can keep the GUI open and use either the shell or the GUI interface as appropriate to the desired tasks.

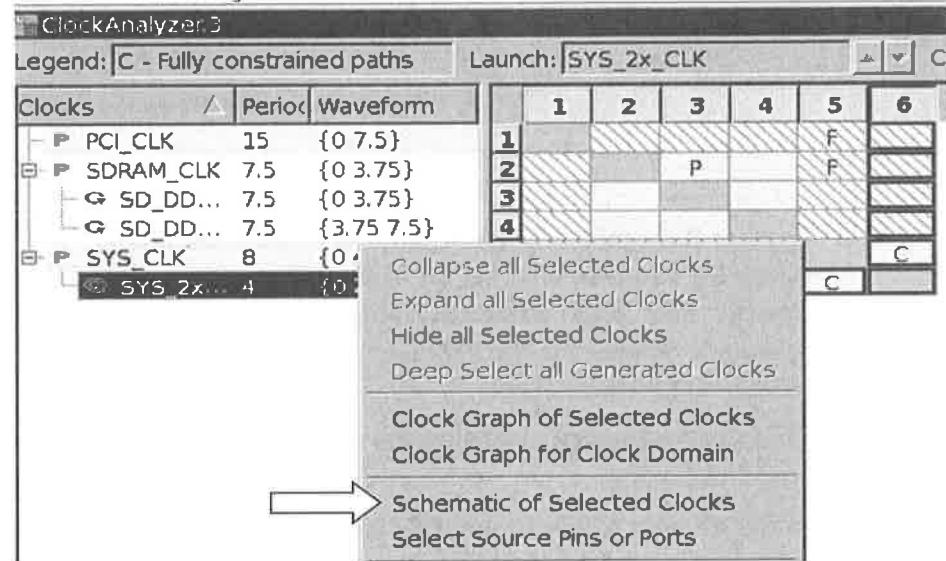

2. Look at clock domain crossings: Open the “clock domain matrix” from the pull-down menu: **Clock → Clock Analyzer**.

The *ClockAnalyzer* window that opens (expand if needed by clicking on the plus signs to the left of the clocks) should match the information from **check\_timing** when reporting the clock crossings in the design. Mouse over the blocks in the matrix to see information on what type of false paths exist. It is sometimes easier to digest this information as a graphical matrix table in comparison to the text output from **check\_timing -override clock\_crossing -verbose**.

The left part of the window lists each master clock and any generated clocks that are created from each master clock.

**Question 6.** What is the master clock for **SYS\_2x\_CLK**?

.....

**Question 7.** **SYS\_2x\_CLK** is defined on which pin/port (its “source”)? (note: you may have to drag the clock matrix out of the way, exposing more columns of information about the clocks)

.....

**Question 8.** The master clock for **SYS\_2x\_CLK** is defined on which pin/port?

.....

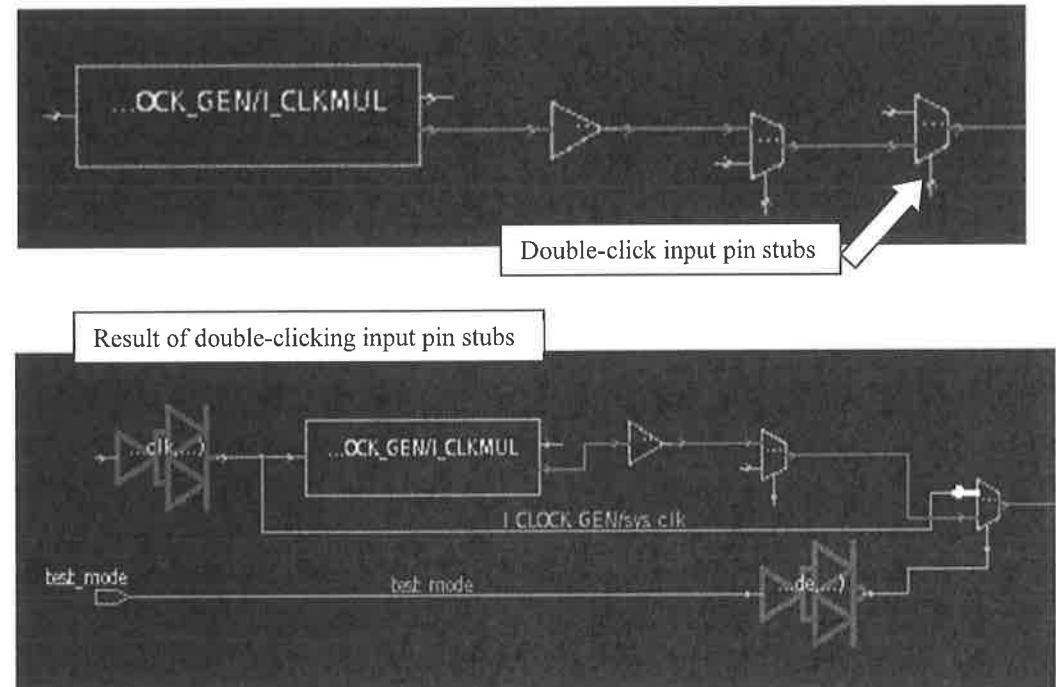

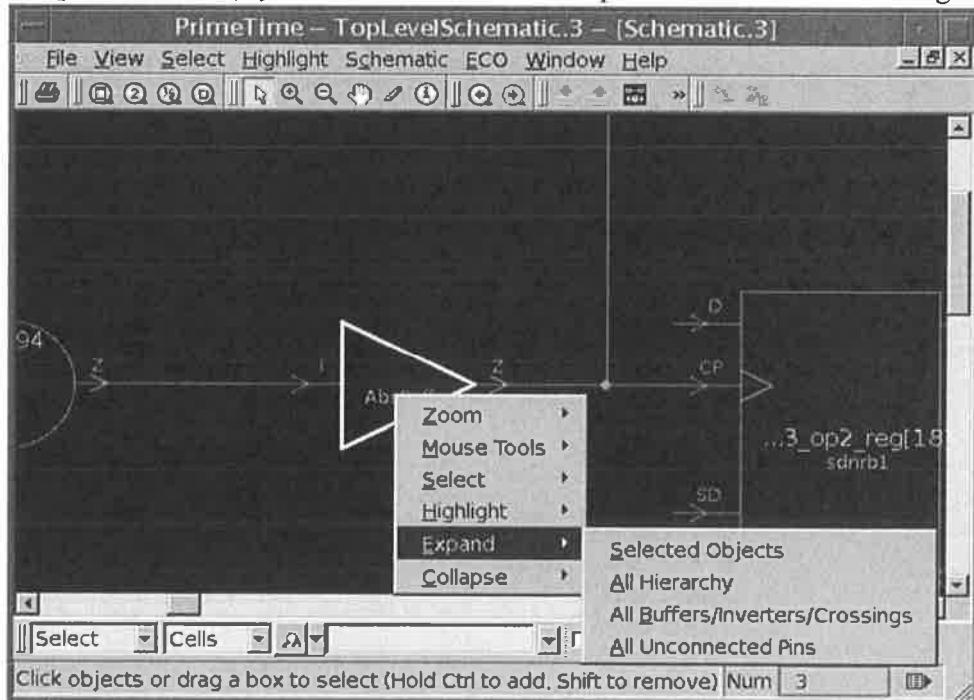

3. Explore in more detail by displaying the clock schematic for **SYS\_2x\_CLK**: select the clock, then right mouse button->Schematic of Selected Clocks. Expand the fanin for the schematic for the MUX called **I\_CLOCK\_GEN/U20** [Hint: To locate/highlight U20, use Select -> By Name] by double-clicking the input stubs, as shown in the following screen captures. Continue the double clicks until the fanin is exhausted [Example: an input port

has been reached]

**Question 9.** What port is connected to the select pin of the MUX I\_CLOCK\_GEN/U20?

## Lab 4

**Question 10.** Does seeing the schematic give you insight into the clocking scheme for test?

.....

4. Explore clock relationships with the abstract clock graph: Close the schematic window, then, on the TopLevel window, select **Clock-> Clock Graph for All Clocks**. If necessary, display a toolbar next to the schematic by pressing the F8 key. Display various elements by checking the toolbar and pressing Apply.

5. Find a pair of muxed clocks: In the Abstract Clock Graph toolbar, select Mux and click Apply.

6. In the Abstract Clock Graph, find instance I\_CLOCK\_GEN/U10 of mx02d1. [Hint: To locate/highlight U10, use Select -> By Name]

**Question 11.** What clocks drive I\_CLOCK\_GEN/U10?

.....

7. From the clock graph window, ‘zoom into’ an interesting object by displaying a schematic for it: Select I\_CLOCK\_GEN/U10, then **Schematic → Schematic View**.

**Question 12.** What port drives the select line to I\_CLOCK\_GEN/U10?

.....

8. Go back to the Abstract Clock Graph.

**Question 13.** From the abstract clock graph window, is it possible to open and display the same clock schematic for SYS\_2x\_CLK you displayed in the clock analyzer [Right Click on SYS\_2x\_CLK and find the option]?

.....

9. Close the *Clock Analyzer* window by clicking on the small “X” in its upper right corner.

10. Close the *Clock Schematic* and *Clock Analyzer* windows by clicking on the small “X” in the upper right corner.

### Task 3. Use the GUI to explore detail of timing paths

Investigate paths between launch and capture clocks – in this case, you will look at network latency for the launch and capture paths clocked by SYS\_CLK.

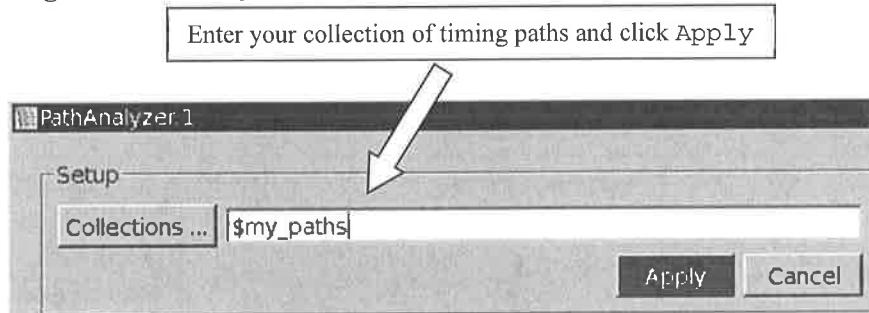

1. Propagate all the clocks to have the clock network delays calculated by Primetime before examining paths, by executing these commands in the shell, which remains open behind the GUI (this will take a minute or so to complete). Tell PrimeTime to save the arrival times for all pins (this is what you will examine). Then, define a collection of timing paths to examine.

```

set_propagated_clock [all_clocks]

set timing_save_pin_arrival_and_slack true

update_timing

set my_paths [get_timing_paths -max 10 -group SYS_CLK

-path full_clock_expanded]

```

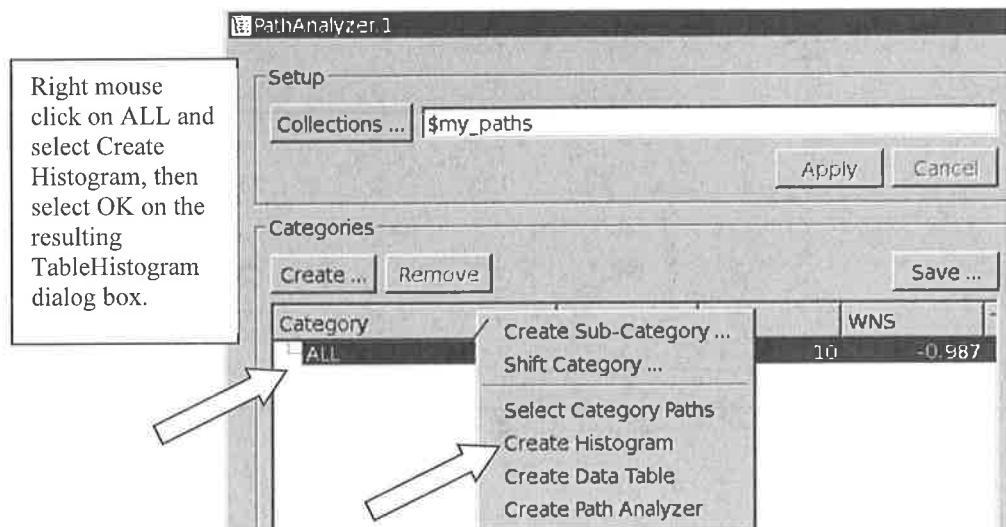

2. Enter your collection of violating paths from the pull-down menu **Timing** → **Path Analyzer**.

3. Bring up a histogram of your ten timing paths.

## Lab 4

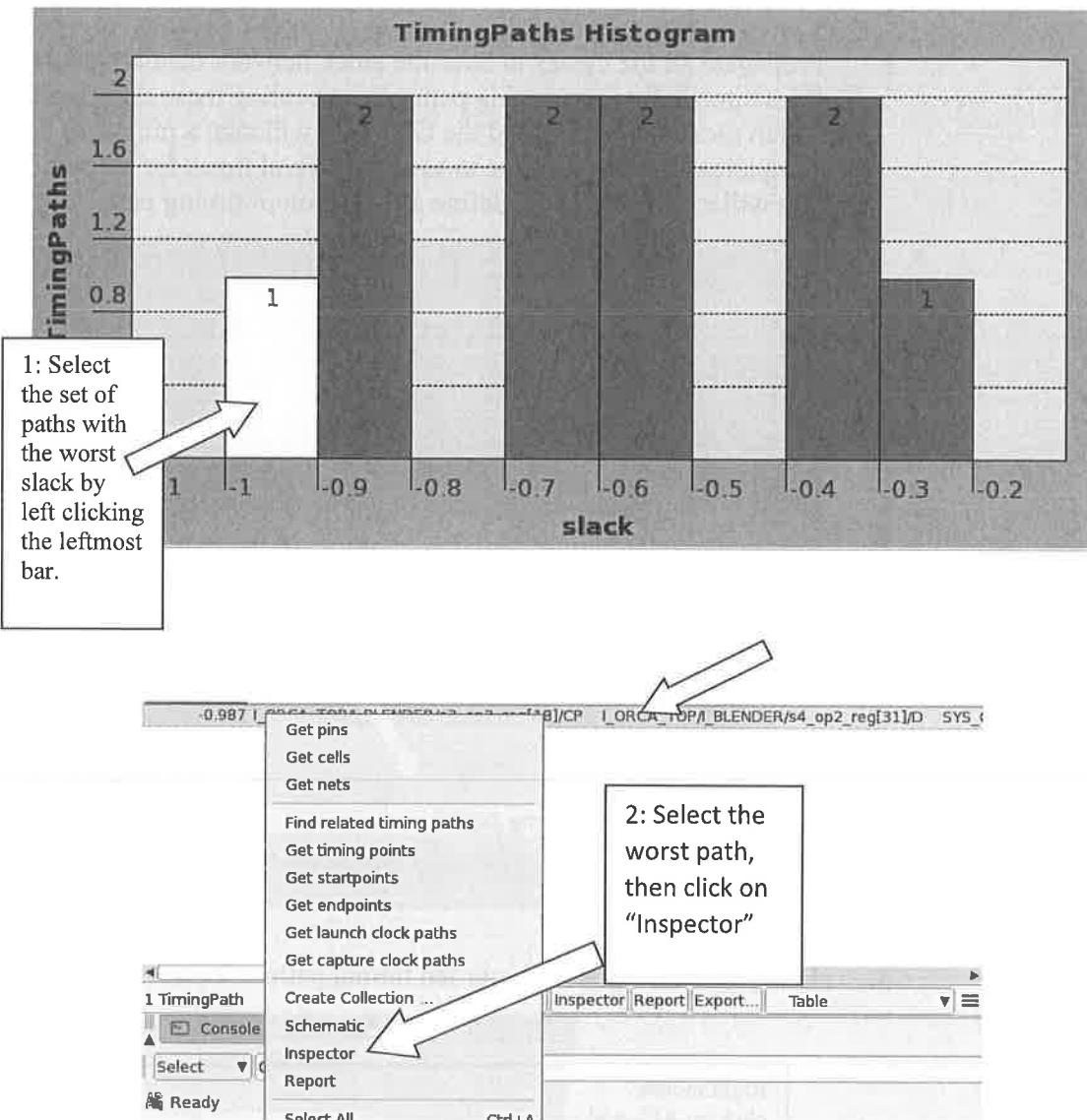

4. From the histogram, bring up the Path Inspector on a selected path.

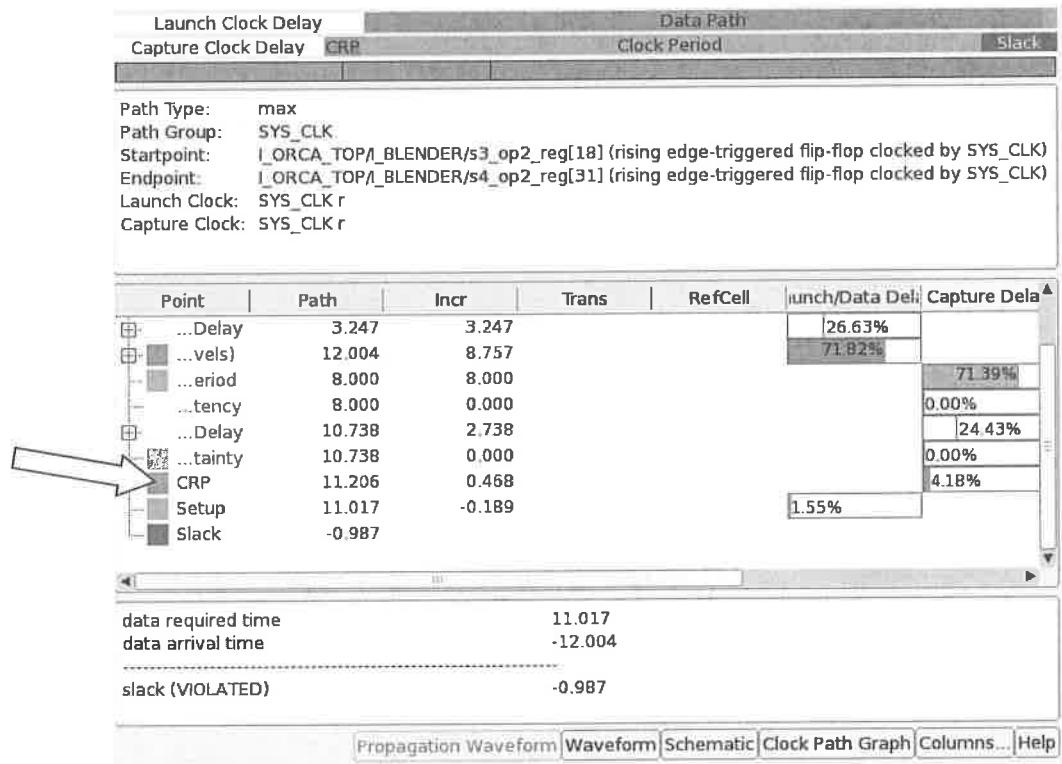

5. In the Path Inspector, examine clock reconvergent pessimism: In the data required and data arrival section, scroll down until you find CRP. Then, scroll across until you find the percent of delay for the CRP.

**Question 14.** What percent of the capture delay comes from CRP?

.....

**Question 15.** Is this percent representative of all designs?

.....

## Lab 4

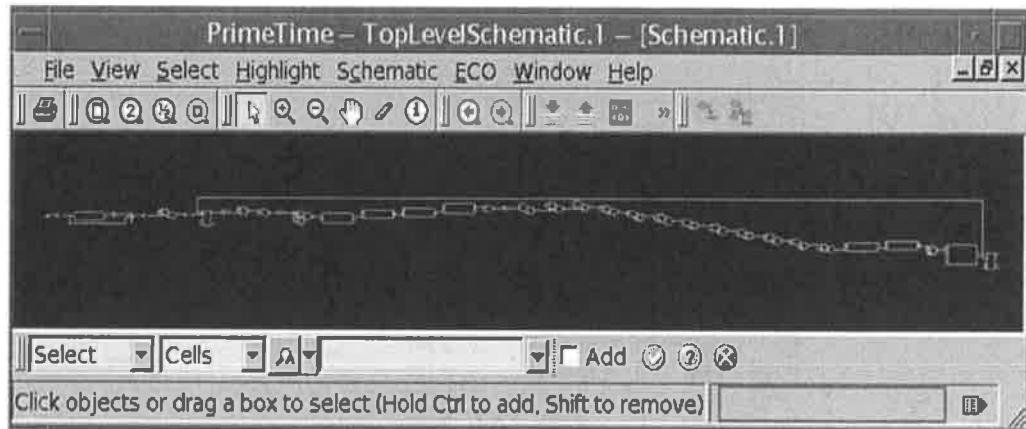

6. Look at a schematic of the path by clicking on the Schematic tab on the bottom of the path inspector window.

7. In the schematic window, find the CRP (clock reconvergent pessimism) point. This is the last pin before the launch and capture paths diverge.

**Note:** Mouse “gestures” or “strokes” are available for easier zooming: While pressing the middle mouse button drag the cursor vertically for ‘zoom full’; Drag diagonally up across an object to zoom in, and down across an object to zoom out.

8. To see arrival times on this pin, if necessary, you may have to first ‘expand’ the pin’s buffer. (By default, PrimeTime ‘collapses’ buffer trees into a single

9. View the arrival times (and any other attributes of interest) by selecting the output pin of the buffer just before the register, then by selecting View->Property

**Question 16.** How wide is the arrival window for the buffer output pin?

.....

**Question 17.** Does this match what we saw earlier in the data arrival data required section of the path inspector?

.....

10. Examine the path waveform: Click on the Waveform tab at the bottom of the Path Inspector window.

**Question 18.** What can you add to the waveforms by clicking the right mouse button in the waveform window?

.....

11. Close the GUI while keeping the original pt\_shell session going in the terminal window:

File → Close GUI (in the main GUI window)

Or

pt\_shell> stop\_gui (in the pt\_shell window)

12. Exit PrimeTime.

## Lab 4

### Task 4. Report a False Violation

1. Bring up PrimeTime and restore the saved session

`orca_savesession_violations`

2. Determine the number and type of timing violations in ORCA:

```

report_analysis_coverage

```

**Question 19.** How many, and what kind of violations does ORCA have?

.....

3. Generate a “short” timing report for the worst slack for an `out_setup` timing check.

**Question 20.** How will you identify the endpoint port which has the worst slack for `out_setup` (use the job aid labeled “Timing Reports” for help recalling the two appropriate switches)?

.....

**Question 21.** Which clocks (launch and capture) are involved in this violation?

.....

*From task 1, you know that `SD_DDR_CLK` is a generated clock defined at an output port. The purpose of defining outgoing clocks is that PrimeTime calculates source latency for this clock and include this latency as part of the data required time.*

4. Look at the data required time section of the timing report from the last step and notice that no clock latency is reported.

Confirm this with the following command:

```

# This report will return nothing as PrimeTime has not

# calculated source latency for SD_DDR_CLK

pt_shell> report_clock -skew SD_DDR_CLK

```

**Question 22.** Why has PrimeTime not calculated source latency for the outgoing clock `SD_DDR_CLK`?

.....

*After speaking with the designer, it turns out there was a miscommunication. The designer was expecting you to turn on a variable that will propagate all clocks!*

5. There is a variable that can be used to make all clocks propagated. Use the Tcl procedure `aa` to help you identify the appropriate variable:

```

aa propagate

```

**Question 23.** What is the name of this variable?

.....

**Question 24.** Using a man page, explain what this variable will do?

.....

6. Use the man page for `check_timing` to find the name of the additional check that will flag all ideal clocks.

The following command opens the man page in a pop-up window with a scroll bar that simplifies viewing long reports.

```

pt_shell> vman check_timing

```

*The above command is an alias created in the `.synopsys_pt.setup` file. It uses a command called `view` that is available on SolvNet, Doc Id 014947.*

*The alias `vman` will not work if the “`wish`” executable, the main executable in the `Tk` package, is not installed and made available in your lab environment*

**Question 25.** How will you modify `check_timing` to add a check to validate that all clocks are propagated?

.....

7. Quit *PrimeTime*.

## Lab 4

### Task 5. Re-Execute the Run Script to reduce violation

1. You are provided with the file `./scripts/orca_pt_variables.tcl` that will accomplish the following two things.

- Adds to the default checks performed by `check_timing` the check that will flag ideal clocks.

- All created clocks will be created as propagated clocks.

2. Execute the run script `./RUN.tcl` from the `lab4_clocks` Unix directory

Log the results to the log file `run.log`.

```

unix> pt_shell -f ./RUN.tcl | tee -i run.log

```

3. Invoke PrimeTime and restore the newly saved session in the Unix directory

`./orca_savesession`

4. Use the appropriate commands to confirm the information below:

- The `out_setup` violations have been reduced.

- All clocks are propagated.

- Execute `check_timing` to confirm it is performing its default checks in addition to the check for ideal clocks.

- The source latency is now calculated for `SD_DDR_CLK`.

- The timing report to `sd_DQ[3]` includes this calculated source latency.

*There will be additional violations (more setup violations as well as out\_hold violations) that you can ignore.*

5. Quit PrimeTime.

*This completes lab 4. Return to lecture.*

## Answers / Solutions

**Question 1.** How many clocks are in this design and how many of these are generated?

This information can be gathered from `report_clock`, or using the following commands.

```

pt_shell> sizeof_collection [all_clocks]

6

pt_shell> sizeof_collection [get_generated_clocks *]

3

```

**Question 2.** Which input ports have defined, master clocks?

| pt_shell> rpt_clock_ports      |           |                                     |              |  |

|--------------------------------|-----------|-------------------------------------|--------------|--|

| Port Name                      | Direction | Clock Name                          | Is Generated |  |

| <code>pclk</code>              | in        | <code>PCI_CLK</code>                | false        |  |

| <code>sys_clk</code>           | in        | <code>SYS_CLK</code>                | false        |  |

| <code>sdr_clk</code>           | in        | <code>SDRAM_CLK</code>              | false        |  |

| <code>sd_CK</code>             | out       | <code>SD_DDR_CLK</code>             | true         |  |

| <code>sd_CK<sub>n</sub></code> | out       | <code>SD_DDR_CLK<sub>n</sub></code> | true         |  |

**Question 3.** Which output ports have defined, outgoing clocks?

From the same report, `sd_CK` and `sd_CKn`.

**Question 4.** Are the clocks propagated or ideal?

Use `report_clock` to see that all the design clocks are ideal.

**Question 5.** Which 3 clock pairs have constrained timing paths?

```

pt_shell> check_timing -over clock_crossing -verbose

Information: Checking 'clock_crossing'.

Information: There are 4 clocks having domains interacting.

* all paths are false paths

# part of paths are false paths

From Clock           Crossing Clocks

-----

PCI_CLK              SYS_CLK*

SDRAM_CLK            SD_DDR_CLK#, SYS_CLK*

SYS_2x_CLK           SDRAM_CLK*, SYS_CLK

SYS_CLK              PCI_CLK*, SDRAM_CLK*, SYS_2x_CLK

```

**Question 6.** What is the master clock for **SYS\_2x\_CLK**?

**SYS\_CLK**

**Question 7.** **SYS\_2x\_CLK** is defined on which pin/port (its “source”)?

**I\_CLOCK\_GEN/I\_CLKMUL/CLK\_2X** (You may have to drag the window containing the matrix out of the way in order to see the source pins)

**Question 8.** The master clock for **SYS\_2x\_CLK** is defined on which pin/port?

**sys\_clk**

**Question 9.** What port is connected to the select pin of the MUX **I\_CLOCK\_GEN/U20**?

**test\_mode**

**Question 10.** Does seeing the schematic give you insight into the clocking scheme for test?

Yes – two clocks come into the mux: one from the clock generator, one directly from the port. The **test\_mode** port controls the select line, making it possible to bypass the clock generator during test mode and letting the design be driven directly from the port.

**Question 11.** What clocks drive **I\_CLOCK\_GEN/U10**?

**SYS\_CLK and SYS\_2x\_CLK**

**Question 12.** What port drives the select line to I\_CLOCK\_GEN/U10?

power\_save

**Question 13.** From the abstract clock graph window, is it possible to display the same clock schematic you displayed in the clock analyzer?

Yes. Select the clock SYS\_2x\_CLK (you may have to zoom in to select just the clock), then press right mouse button and select Schematic for Selected Clocks. You may have to expand input or output stubs (by double clicking on them) to get the exact same schematic.

**Question 14.** What percent of the capture delay comes from CRP?

4.18%

**Question 15.** Is this percent representative of all designs?

No, this number is dependent on the particular design and on the particular path.

**Question 16.** How wide is the arrival window for the buffer output pin?